# 3262A **TV Sync Generator**

MOS Memory Products

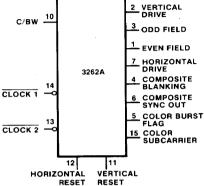

Logic Symbol

#### Description

The 3262A is a sync pulse generator that produces the necessary outputs for synchronizing television proadcast information. These outputs include Horizontal Drive, Vertical Drive, Composite Sync, Composite Blanking, and Even and Odd Fields. all of which are provided in the format specified by RS170EIA Standard Output Signals. The Color Subcarrier (3.58 MHz) and the Color Burst Flag outputs are provided for color operation. All waveforms are derived from a low-voltage two-phase clock (for color operation) or a single-phase clock (for black and white operation). All outputs except the Color Subcarrier are capable of driving a TTL load directly. The Color Subcarrier is designed to drive a capacitive load. The 3262A is a monolithic integrated circuit manufactured with Isoplanar p-channel silicon gate technology.

- **COLOR OR BLACK/WHITE OPERATION**

- **ALL COUNTERS SYNCHRONOUS**

- **PULSE WIDTHS DERIVED DIGITALLY**

- **OUTPUTS DRIVE TTL DIRECTLY (EXCEPT COLOR SUBCARRIER)**

- SEPARATE VERTICAL AND HORIZONTAL RESET

## **Applications**

- **CAMERA LOGIC REPLACEMENT**

- **HOME TV GAMES**

- **VIDEO TAPE RECORDS**

- **VIDEO TERMINALS**

#### **Absolute Maximum Ratings**

All Inputs (Note) -20 V to +0.3 V -20 V to +0.3 V V<sub>DD</sub> and Outputs -6 V to +0.3 V DC Output Current (output LOW) <10 mA -55°C to 150°C Storage Temperature 0°C to 70°C Operating Temperature Maximum Power Dissipation 750 mW

All Voltages with respect to Vss

Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

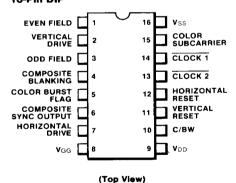

V<sub>SS</sub> = Pin 16 V<sub>DD</sub> = Pin 9 V<sub>GG</sub> = Pin 8

#### **Connection Diagram** 16-Pin DIP

| Package     | Outline | Order<br>Code |

|-------------|---------|---------------|

| Ceramic DIP | 6Z      | D             |

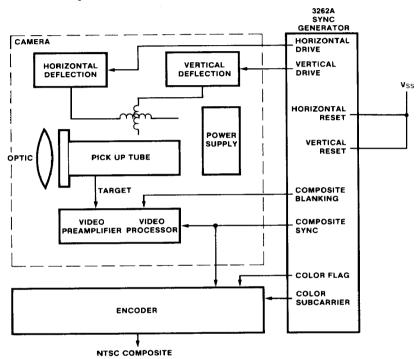

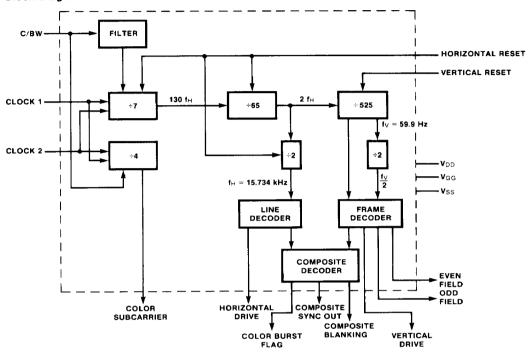

#### **Block Diagram**

#### **Functional Description**

The 3262A block diagram shows the counting and decoding scheme used to generate all output waveforms. The clock frequency is divided down in three steps ( $\div$ 7,  $\div$ 65,  $\div$ 2) and decoded to generate the horizontal drive. A signal at twice the horizontal frequency is divided by 525 to generate the vertical drive. The Color Subcarrier is generated by a  $\div$ 4 Johnson counter driven directly from the input clock. This is approximately a sinusodial signal. Pulses at the horizontal and vertical frequencies are combined in the composite decoder to generate the outputs Composite Sync, Composite Blanking, and Color Burst Flag.

For use in special applications, the 3262A provides a 30 Hz pulse at the start of the field (Odd Field) and again at the start of the next field (Even Field).

Separate Horizontal and Vertical Reset input pins are provided to allow the 3262A to be used in systems requiring gen-lock operation. Tie Horizontal and Vertical Resets to V<sub>SS</sub> when they are not used.

The C/BW input is used to select either color or black and white operation. A logic HIGH applied to C/BW will select color operation; if C/BW is LOW, the  $\div 4$  and  $\div 7$  counters will be bypassed for black and white operation. In addition, the only clock needed for black and white operation is Clock 1; Clock 2 should be tied to Vss. The input frequency should be 2.0475 MHz for normal operation.

C/BW when LOW also resets the Color Subcarrier. If the LOW pulse on C/BW is within the specification for t<sub>RS</sub> — Color Subcarrier Reset Pulse — the color operation for the 3262A will be unaffected.

DC Characteristics  $V_{SS}$  = 5.1 V  $\pm$ 0.25 V,  $V_{GG}$  = -12 V  $\pm$  5%,  $V_{DD}$  = 0 V,  $T_A$  = 0°C to + 70°C

| Symbol          | Characteristic                                     | Min                  | Тур | Max                   | Unit               | Condition                                                                             |

|-----------------|----------------------------------------------------|----------------------|-----|-----------------------|--------------------|---------------------------------------------------------------------------------------|

| VIH             | Input HIGH Voltage                                 | V <sub>SS</sub> -0.8 |     | V <sub>SS</sub> +0.3  | V                  |                                                                                       |

| VIL             | Input LOW Voltage                                  | -5.0                 |     | V <sub>SS</sub> -4.35 | V                  |                                                                                       |

| VoH             | Output HIGH Voltage                                | 2.4                  |     |                       | ٧                  | $I_{OH} = -0.1 \text{ mA}$                                                            |

| V <sub>OL</sub> | Output LOW Voltage                                 |                      |     | 0.4                   | V                  | I <sub>OL</sub> = 1.6 mA                                                              |

| VIHC            | Clock Input HIGH Voltage                           | V <sub>SS</sub> -1.0 |     | V <sub>SS</sub> +0.3  | ٧                  |                                                                                       |

| VILC            | Clock Input LOW Voltage                            | -5.0 V               |     | V <sub>SS</sub> -4.35 | V                  |                                                                                       |

| VSUBCARRIER     | Subcarrier Output Voltage<br>Approximate Sine wave | 0.5                  |     |                       | V <sub>pk-pk</sub> | $C = 10 \text{ pF to V}_{DD}$<br>$R = 10 \text{ k}\Omega \text{ to V}_{DD}$<br>Note 1 |

| liN             | Input Leakage Current                              |                      | 1.0 |                       | μΑ                 | V <sub>IN</sub> = 0 V                                                                 |

| IDD             | V <sub>DD</sub> Current                            |                      | 14  |                       | mA                 |                                                                                       |

| lgg             | V <sub>GG</sub> Current                            |                      | 40  |                       | mA                 |                                                                                       |

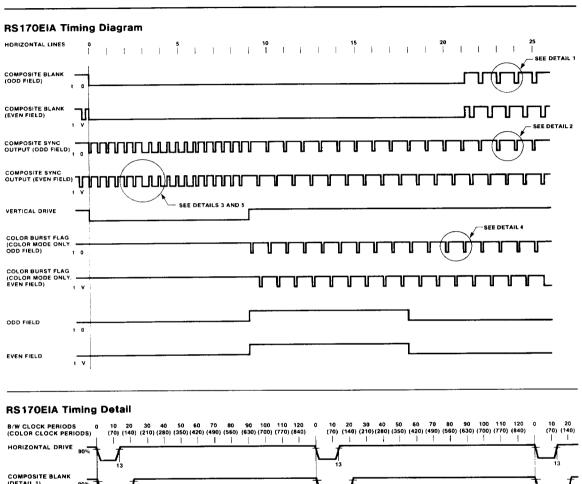

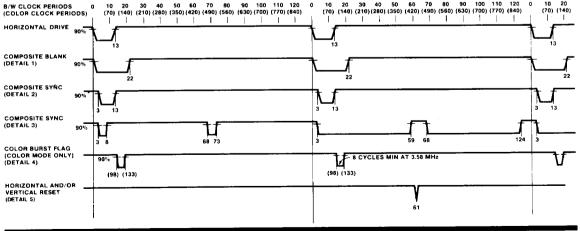

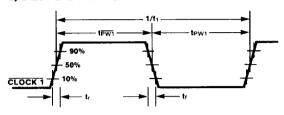

AC Characteristics  $V_{SS}=5.1~V~\pm0.25~V,~V_{GG}=-12~V~\pm~5\%,~V_{DD}=0~V,~C_L=10~pF,~1~TTL~Load~(1.6~mA),~T_A=0^{\circ}C~to+70^{\circ}C~(See~Timing~Diagrams)$

| Symbol         | Characteristic                        | Min  | Тур      | Max  | Unit | Condition                              |

|----------------|---------------------------------------|------|----------|------|------|----------------------------------------|

| f              | Input Frequency Color                 | 13.3 | 14.31818 | 15.4 | MHz  | $t_{\rm f},t_{\rm f}\leq 5~{\rm ns}$   |

| f <sub>1</sub> | Input Frequency<br>Black/White        | 1.5  | 2.0475   | 2.2  | MHz  | $t_{\rm f},t_{\rm f}\leq 20~{\rm ns}$  |

| tpw1           | B/W Clock LOW Time                    | 200  | 215      | 230  | ns   | $t_r$ , $t_f \le 20 \text{ ns}$        |

| tPW1           | B/W Clock HIGH Time                   | 200  | 215      |      | ns   | $t_{r}$ , $t_{f} \leq$ 20 ns           |

| tpw2           | Color Clock LOW Time                  | 30   | 35       | 40   | ns   | $t_{\rm f},t_{\rm f} \leq 5~{\rm ns}$  |

| tPW2           | Color Clock HIGH Time                 | 30   | 35       |      | ns   | $t_{r}$ , $t_{f} \leq 5$ ns            |

| tov            | Color Clock Overlap Time              |      |          | 5    | ns   |                                        |

| thr PW         | Horizontal Reset<br>Pulse Width       | 200  |          |      | ns   | $t_{\rm f},t_{\rm f} \leq 20~{\rm ns}$ |

| tvr pw         | Vertical Reset Pulse Width            | 200  |          |      | ns   | $t_r$ , $t_f \le 20$ ns, Note 2        |

| tcsr           | Color Subcarrier<br>Reset Pulse Width | 130  |          | 200  | ns   | $t_{\rm f},t_{\rm f}\leq 20~{\rm ns}$  |

#### Notes

- Subcarrier Output should be dc blocked with .01 µF before loading.

- 2. If tHR occurs simultaneously;

- if  $t_{HR}$  does not occur,  $t_{VR}$  = 400 ns min.

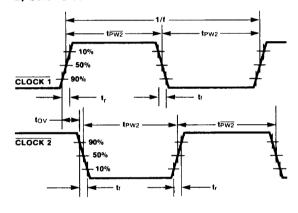

## **Clock Timing Diagrams**

## a) Black and White Clock

# b) Color Clocks

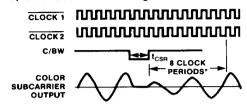

## c) Color Subcarrier Timing and Reset Detail

\*Maximum subcarrier amplitude attained within 8 color clock periods following rising edge of C/BW.

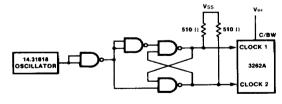

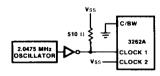

## **Clock Generator Circuitry**

#### a) Color Clocks

#### b) Black and White Clock

## **Applications**

## TV Camera System